# 13kV級 SiC-MOSFETを使用したパルスパワー電源の開発

# DEVELOPMENT A PULSED POWER SUPPLY UTILISING 13 KV CLASS SIC-MOSFETS

岡村勝也<sup>#, A),B)</sup>, 限元大輝 <sup>C)</sup>, 海東達也 <sup>D)</sup>, 徳地明 <sup>E)</sup>, 林秀原 <sup>E)</sup>, 内藤富士雄 <sup>A),B)</sup>, 高山健 <sup>A)</sup>, 北井秀憲 <sup>F)</sup>, 道越久人 <sup>F)</sup>, 福田憲司 <sup>F)</sup>, 坂本邦博 <sup>F)</sup>

Katsuya Okamura<sup>#, A),B)</sup>, Daiki Kumamoto<sup>C)</sup>, Tatsuya Kaito<sup>D)</sup>, Akira Tokuchi<sup>E)</sup>, Soowon Lim<sup>E)</sup>, Fujio Naito<sup>A),B)</sup>, Ken Takayama<sup>A)</sup>, Hidenori Kitai<sup>F)</sup>, Hisato Michikoshi<sup>F)</sup>, Kenji Fukuda<sup>F)</sup>, Kunihiro Sakamoto<sup>F)</sup>

A)High Energy Accelerator Research Organization (KEK)

B) SOKENDAI

C)Nagaoka University of Technology

D)Chiba Institute of Technology

E)Pulsed Power Japan Laboratory Ltd. (PPJ)

F)National Institute of Advanced Industrial Science and Technology (AIST)

## Abstract

Switching characteristics of the 13 kV SiC-MOSFET developed by Tsukuba Power Electronics Constellations (TPEC) was investigated. With the conditions of drain voltage of 10 kV and load resistance of 1 k $\Omega$ , turn on loss Eon, turn off loss Eoff, rise time Tr and fall time Tf were 1.7 mJ, 1.1 mJ, 64 ns, 75 ns, respectively. As to gate charge characteristics, required electric charge to increase gate source voltage until 20 V was about 80 nC. Thereafter 2s-12p switch array was designed and assembled. With dc voltage of 14 kV and load resistance of 28  $\Omega$ , 490 A pulse operation was confirmed. However current rise time (10 % - 90 %) was 430 ns, the value of which was 4 times slower than the value of the intrinsic performance of the single device. This slow switching speed was caused by a large gate resistance and shunt capacitor for preventing false operation. Improvement is necessary in the future.

## 1. はじめに

加速器には種々のパルス電源が要求される。パル スの発生には高速、高電圧、大電流のスイッチが必 要であり、歴史的に見て初期の段階においてはス パークギャップスイッチが使用され、やがてサイラ トロンに代表される電子管に置き換わり、さらに信 頼性を向上させるために半導体スイッチの導入が図 られ、現在に至っている。しかし、半導体スイッチ は個々の素子の耐電圧が十分でなく数 10 個もの素 子を直列接続する必要がある。今後、医療用途や産 業用に広く加速器を適用していくにあたって、電源 の構成部品点数を減らし、信頼性向上と小型化を図 ることは必須条件である。そこで我々は TPEC (Tsukuba Power Electronics Constellations)において開 発された SiC-MOSFET を利用し、従来の Si 半導体 を使用したものに比べて格段に小型化を図ったパル ス電源の開発に着手している。

# 2. SiC-MOSFET

SiC は従来から広くパワーデバイスとして用いられている Si と比して、(1)3倍のバンドギャップ、(2)10 倍高い絶縁破壊電界、(3)2倍高い融点、(4)3倍の熱伝導度を有し、高電圧、大電力に適した次世代のパワーデバイス材料として注目されてきた。特

\*katsuya.okamura@j-parc.jp

に近年高速スイッチングに適した MOSFET の開発が著しく進展し、我々も 3.3 kV 耐圧の素子を用いた高繰り返しパルス電源の開発に取り組んでいる[1,2]。さらに今回は従来の Si デバイスでは全く不可能であった 13 kV 級素子 [3]を用いたパルス電源の開発について報告する。Figure 1 に本研究で用いた SiC-MOSFET の外観を示す。形状としてはTO-268-2L と称される標準パッケージとほぼ同等のものである。

Figure 1: An external view of the SiC-MOSFET.

## 3. 素子単体特性

# 3.1 スイッチング波形

最初に素子単体でのスイッチング試験を実施した。

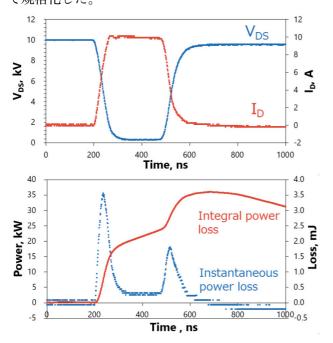

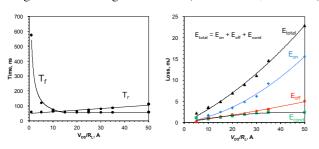

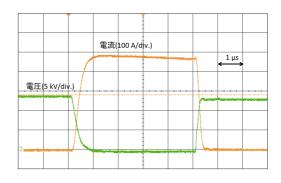

電圧、電流波形、損失の各波形を Figure 2 に示す。但し、ドレイン電圧 10~kV、負荷抵抗  $1~k\Omega$ である。さらに負荷抵抗を変化させた時のスイッチング時間、スイッチング損失の変化を Figure 3~kに示す。但し、Figure 3~kにおいて横軸は(ドレイン電圧/負荷抵抗)で規格化した。

Figure 2: Switching waveforms. (VDS: 10 kV, RL:  $1 \text{ k}\Omega$ )

Figure 3: Switching loss and switching time.

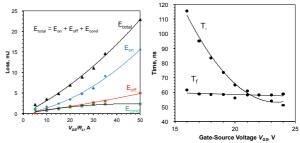

## 3.2 ゲート駆動電圧依存性

MOSFET においてゲート駆動電圧はオン時のドレインーソース間抵抗に影響を与える重要なファクターである。Figure 4 にスイッチングロスとスイッチング時間のゲート駆動電圧依存性を示す。この結果より、本 FET を駆動するためには少なくとも20V以上のゲート電圧が必要と考えられる。

Figure 4: Gate voltage dependency of switching loss and switching time. (VDS: 10 kV, RL:  $1 \text{ k}\Omega$ )

Figure 5: Estimation of output capacitance from the fall time.

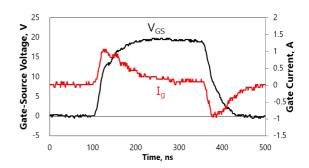

Figure 6: Gate voltage and gate current waveform. (upper:  $V_{LS}=0$  V, lower:  $V_{LS}=5$  kV)

## **PASJ2018 WEP067**

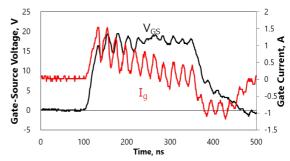

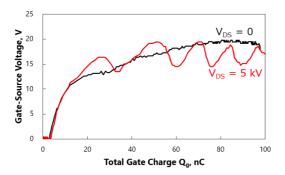

Figure 7: Cumulated gate charge characteristics.

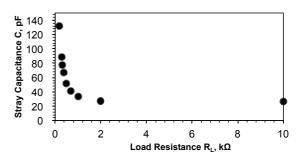

#### 3.3 寄生出力容量

MOSFET ターンオフ時のスイッチングスピードに影響を与える要素として出力容量がある。出力容量が存在する時、出力容量と負荷抵抗の積で決まる時定数がターンオフ時の立ち上がり時間を制約する。Figure 5 に負荷抵抗を変えた時の電圧立ち上がり時間から推定した出力容量を示す。負荷抵抗が比較的小さくなるほど出力容量が大きくなっていくように見えるが、これは負荷抵抗が小さい時には CR の時定数だけではなく供試 MOSFET の本質的なスイッチング特性によって立ち上がり時間が制約されているためと考えられる。一方、負荷抵抗が大きくなると出力容量は一定値(27 pF)に収束する。したがって供試 MOSFET の出力容量は 27 pF であると評価される。

## 3.3 ゲートチャージ特性

MOSFET はゲートソース間に印加される電圧によって駆動されるが、そのドライバー回路を設計する上で絶縁されたゲートを充電するために必要な電荷量を知る必要がある。Figure 6 にゲート電圧波形、ゲート電流波形の例を、Figure 7 に電流波形の積分から求めたゲート電荷の例を示す。ゲート電圧を20 Vまで上昇させるためには80 nC 程度の電荷が必要であることがわかる。

# 4. スイッチアレーの試作と評価

## 4.1 スイッチアレーの構成

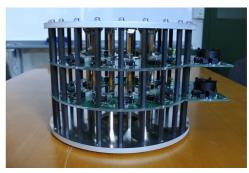

素子単体ではパルス電源として使用するためには電圧、電流の能力が不足であるため、直並列することが不可欠である。今回は SiC-MOSFET を2直列、12並列に接続したスイッチアレーを試作した。直並列にあたって、円板状のプリント基板の周方向に12個の素子を配置して並列とし、この基板をスタックすることによって直列接続とした Figure 8 に基板と完成したスイッチアレーを示す。

Figure 8: External view of the switch board and stacked switch array.

組み立て後の大きさは直径 300 mm x 高さ 250 mm の円筒形である。

#### 4.2 スイッチング試験

直流充電電圧 14 kV、負荷抵抗 28 Qの時のスイッチング波形を Figure 9 に示す。この時、電流の立ち上がり時間(10 % - 90 %)は 430 ns であった。この値は素子単体での立ち上がり時間の約 4 倍である。このように立ち上がり時間が遅くなった原因はスイッチアレーの試験において誤動作が発生したために、ゲート-ソース間に静電容量を追加した、ゲートも可抵抗の値を大きくするなどの対策をとってゲートを遅くしたことが大きな要因となっていると考えられる。今後、SiC-MOSFET の本来の性能を発揮させるためにはゲート電圧波形の立ち上がりを悪化させずに誤動作を防ぐことが大きな課題である。

Figure 9: Switching waveform of the SiC-MOSFET switch-array.

## 5. まとめ

- TPEC において開発された 13 kV SiC-MOSFET のパルス通電特性を調査し、ドレイン電圧 10 kV、負荷抵抗 1 kΩ において、ターンオン損失 1.7 mJ、ターンオフ損失 1.1 mJ、上昇時間 64 ns、下降時間 75 ns 等の諸量を得た。

- ゲート電荷特性においてはゲート電圧を 20 V まで上昇させるために必要な電荷量は 80 nC であった。

- 本 FET を 2 直列 12 並列に接続した高電圧スイッチアレーを設計、製作した。

- 試作したスイッチアレーを用いて、直流電圧 14 kV、負荷抵抗 28Ω のスイチング実験を 行ったところ、490 Aのパルス通電を行うこと ができた

- スイッチアレーのパルス通電において電流の上昇時間は 430 ns と、素子単体の時の結果よりも4倍遅くなった。この原因は誤動作防止のためにゲートに直列抵抗と並列キャパシターを入れたことに起因すると考えられる。今後スイッチ性能を犠牲にせずに誤動作を防止することが必要である。

## 謝辞

本研究の一部は、共同研究体「つくばパワーエレクトロニクスコンステレーション (TPEC)」の事業として行われた。

# 参考文献

- [1] K. Okamura *et al.*, "Development of an Induction Accelerator Cell Driver Utilizing 3.3 kV SiC-MOSFETs", Proceedings of IPAC2017, Copenhagen, Denmark, pp. 3388-3390.

- [2] K. Okamura et al., "Development of an Induction Accelerator Cell Driver Utilizing 3.3 kV SiC-MOSFETs", Proceedings of the 14th Annual Meeting of Particle Accelerator Society of Japan, Sapporo, Japan, Aug. 1-3, 2017, pp. 476-480.

- [3] H. Kitai *et al.*, "Low on-Resistance and Fast Switching of 13-kV SiC MOSFETs with Optimized Junction Field-Effect Transistor Region", Proceedings of the 29th International Symposium on Power Semiconductor Dvices & ICs, Sapporo, pp. 343-346.