# J-PARC リニアック LLRF システムの現状 STATUS OF THE J-PARC LINAC LLRF SYSTEM

二ツ川 健太 \*A), 方志高 A), 福井佑治 A), 篠崎信一 B), 溝端仁志 B), 佐藤福克 C)

Kenta Futatsukawa\* A), Zhigao Fang A), Yuji Fukui A),

Shinichi Shinozaki B), Satoshi Mizobata B), Yoshikatsu Sato C)

A) High Energy Accelerator Research Organization

B) Japan Atomic Energy Agency

C) Nippon Advanced Technology Co., Ltd.

## Abstract

In the J-PARC linac, the LLRF system with the digital feedback (DFB) and the digital feedforward (DFF) was adopted for the satisfaction of amplitude and phase stabilities and is was operated without serious problems. However, is has been used since the beginning of the J-PARC and are more than ten years into the development. The increase of the failure frequency for this system is expected. In addition, it is difficult to maintain it for some discontinued boards of DFB and DFF and the older OS and developing environment of software. Therefore, we are starting to study the new LLRF system of the next generation. In the present, we are exploring several possibilities of a new way and investigating each advantage and disadvantage. The project and the status of the development for the new system in the J-PARC linac LLRF are introduced.

#### 1. はじめに

J-PARC リニアックの LLRF は, 324MHz の空洞用シ ステム (24 式) と 972MHz の ACS 空洞用システム (25 式) がある。周波数 324MHz のシステムは、J-PARC リニ アックの建設当初に開発され、その実装から10年以上が 経過している [1]。現在, デジタルフィードバック (digital feedback system:以下, DFB) やフィードフォワー ド (digital feedforward system:以下, DFF) を担ってい る cPCI のボードの一部が製造中止になり, 更に開発環 境やそれをインストールできる OS を維持することが 厳しくなってきている (Table 1,2)。そこで、次世代の DFB&DFF システムを開発して、その機能を移行するこ とを検討している。本開発における制約として、全49 式の現在のシステムを一遍に交換することは厳しいた め、現在のシステムと開発するシステムとで両立できる ことが要求される。現在は移行後のシステムに実装す るために必要な開発事項を具体的に検討して,導入のた めのオフライン試験を実施している。

Table 1: Discontinued Boards for the LLRF System

| RF&CLK board | some ICs were discontinued |

|--------------|----------------------------|

| FPGA board   | discontinued               |

| DSP board    | discontinued               |

| CPU board    | discontinued               |

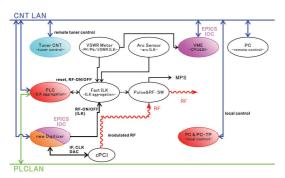

## 2. 現在のLLRFシステム

現在の LLRF システムの概略図を Figure 1 に示す。 現在の LLRF システムでは、cPCI が DFB&DFF の役割 を担っている。LLRF のパラメータを変更する場合は、 現場の PLC タッチパネル (以下, PLC-TP) から PLC を経 由して cPCI に命令する。または、遠隔の場合は VME-CPU が PLC の EPICS-IOC を担っていて、各制御端末か

Table 2: Developing Environments of the LLRF System

| host program     | RedHat8 gcc compiler Ver3.2    |  |

|------------------|--------------------------------|--|

| server PC OS     | CentOS5.5                      |  |

| GUI              | python2.4, wxPython2.6         |  |

| FPGA             | Xilinx ISE Ver6.2i             |  |

| DSP              | TI Code Composer Studio Ver2.1 |  |

| developing PC OS | windows2000                    |  |

ら PLC を経由して cPCI に命令する。cPCI で測定した振幅や位相、離調度や  $Q_L$  などのモニタ値に関しても、全て PLC を経由して EPICS レコード化されている。また、空洞の自動チューナ制御に関しても cPCI で計算した移動量を PLC を経由して、チューナコントローラに命令を送っている。このような PLC 制御に直接関係ない設定及びモニタ値が PLC を経由する現在の構成は、システム開発の時間と労力を大幅に増大させている。 PLCはインターロック (以下、ILK) の管理も行っていることもあり、頻繁にラダーを変更することは望ましい状況ではない。

また、324MHz の PLC は、費用削減を目的にシーケンス CPU が 4 台中 1 台しか有しておらず、マスタースレーブの関係がある。 現在ではシーケンス CPU がそれほど高価ではないこと、頻繁に PLC の電源のオフ/オンをすることもあり、この関係も煩わしくなっている。

## 3. 検討中のLLRFシステム

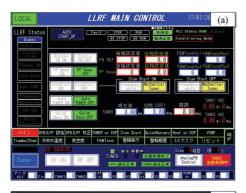

Figure 2 に現在検討している LLRF システムの概略 図を記載する。最初は cPCI のアナログボードは代えずに、生産中止となったデジタルボード (FPGA/DSP ボード、IO ボード、及び CPU ボード)の代わりに新規開発するデジタイザを導入する。新デジタイザは EPICS-IOC を組み込んだシステムを採用する予定であり、EPICS レコード化にするためだけに信号が PLC を経由することはない。PLC ラダーはその大部分が ILK を管理する機

<sup>\*</sup> kenta.futatsukawa@kek.jp

Figure 1: Present LLRF system of the J-PARC linac.

能に専有され,単純で安全な構成となる。一方で,現在のシステムの PLC シーケンスが担っていた機能を他の方法で実現する必要が生じている。

以下, 開発中のシステムの構成, 及び現在計画している機能の移植計画と試験の結果を記載する。

Figure 2: New LLRF system of the J-PARC linac.

## 3.1 新デジタイザの開発

現在、cPICのデジタル系のボードに代わるデジタイザの開発を行っている。現在公示中の一般競争入札案件であるため詳細は割愛するが、当該デジタイザは EPICS-IOC の組込みシステムを採用する予定である。また、現在の cPCI ADC は 4 チャンネルであるの対して、新デジタイザは 8 チャンネル(4 チャンネル:mixer+IQ sampling、4 チャンネル:direct sampling)を予定している。将来的には、現在の空洞間位相監視モニタの役割を取り込むことも想定している。

## 3.2 PLC ラダーの改修

開発中のシステムでは、新デジタイザが EPICS-IOC も担うため、LLRFのパラメータを設定する際に不必要に PLC を経由することはない。また、現在のシステムにあるような簡単なプログラムも PLC シーケンスに埋め込んで制御することはない。また、324MHzのステーションでは、マスタースレーブの関係を改め、全てにシーケンス CPU を設置して全てのステーションをマスターとする予定である。このため、ラダーは大規模な変更を行い、1 ステーション分のラダーの規模は、1/2 から 1/4 程度になると思われる。

#### 3.3 現場.遠隔制御

現在のシステムでは、現場での制御時には PLC-TPで制御すれば良かったため、PLC シーケンサが現場制御と遠隔制御を区別すれば良かった。しかし、開発中のシステムでは、現場/遠隔制御を管理する対称が PLC だけではなく新デジタイザも含まれている。そこで、EPICS ASG (Access Security Group) フィールドを採用して、現場制御の時には現場に設置される PC のみにアクセス許可を与える予定である。加えて、現在のシステムで使用している 現場制御 (local) と遠隔制御 (remote) という状態だけでなく、利用運転中にパラメータ変更を制限した状態(strict)を設ける予定である。softIOC 上で ASGフィールドの動作確認を実施して、意図通りの動作することまで確認できている。

また、現在は、PLC-TPを使用して現場での制御をしている。しかし、開発中のシステムにおいては、PLCだけではなく新デジタイザも制御する必要がある。そのために、端末 PCとディスプレイ、マウス及びキーボードを用意するのが安直には容易ではあるが、ラック内のスペース的にこれらを設置するのは厳しい。そこで、以下の3通りの案を検討した。

- 1. 小型 PC と TP 機能付きディスプレイ

- 2. Raspberry Pi3 (ARM) と TP 機能付きディスプレイ

- 3. PC と TP が一体になった製品 (TPC-E019C10S)

1から3の案を試してメリットとデメリットを比較した結果,製品の安定や CPU パワーなどを考慮して,1の案を第一候補として開発を進めている。

現場制御の GUI は、java をメインとして開発しているが、トレンド表示などには利便性の高い CSS も使用する予定である。 Figure 3(a) に現在の PLC 制御のメイン画面、(b) に java で作成した現在開発中のメイン画面を示す。 現場の制御は本開発に関わっていない人を含めて多人数が使用するため、見た目の変更点を極力抑えるように設計を進めている。

## 3.4 スクリプト動作の導入

Auto-Start\_UP は、空洞が冷えて共振周波数が変動し た状態から定格パワーまで自動で立ち上げる制御ツー ルである [2-4]。現在は, 自動チューナ制御機能を使用 する方法(以下, mechanical tuner)と,可動チューナを固 定して入力周波数を変更して定格までパワーを入れる 方法(以下, frequency shift) を実装している。現状では RFO とチョッパを除いた空洞では後者の方法を採用し て,空洞の立ち上げを行っている。これらは,現システ ムでは PLC ラダーと cPCI に実装されている。一方で、 開発中のシステムでは EPICS の CA を利用して C shell の script で実現させることを検討している。現在でも、 チョッパ空洞などは上記の方法では立上げを行うこと が困難であるため、開発中のシステムでは現在実装され ている mechanical tuner/frequency shift だけでなく, 必 要に応じて空洞の特性に応じた専用の立上げ方法を用 意する予定である。開発中のメイン画面がバックグラ ンドジョブで該当 EPICS レコードのフラグをポーリン グしていて, フラグが上がったときにこのスクリプトを 実行する予定である。現場のメイン画面及び遠隔の端

Figure 3: (a) present and (b) developing main displays of the local control. We are keeping the almost same usability of the two displays.

末の両方から、EPICS レコードのフラグを立てることで 実行できるように準備している。

Table 3 は DTL1, SDTL01 及び ACS01 空洞におい て Auto-Start\_UP のロジック終了までの必要時間の試 験結果を示している。このときは、Auto-Start\_UPは frequency shift 方法で試験を行っている。DTL1 に関して、 現在のシステムが97秒でシーケンスが終了したのに対 して, 開発中のスクリプトが 286 秒と大幅に時間を要 している。これは、定格パワーになった後に直ぐに可動 チューナを動かすというロジックの有無による。実際 に、定格パワー到達までに要した時間(51秒)は現在と 開発中の方法でほとんど大差がなかった。開発中のス クリプトにこのロジックを組込むことは比較的容易で はある。しかし、この状態はあくまでも安定していない と判断したため、開発中のシステムにはこのロジックは 実装しない予定である。EPICS 経由では CA に時間が かかるため、全体的に開発中のスクリプトは現在のシス テムより時間を要しているが、実質この立上り時間が問 題になることはないと考えている。

Table 3: Start-up Time Using the Present System and the Developing Auto-Start\_UP Script at the Stations of DTL1, SDLT01, and ACS01

| station | present system | developing script |

|---------|----------------|-------------------|

| DTL1    | 97 sec         | 286 sec (51 sec)  |

| SDTL01  | 40 sec         | 73 sec            |

| ACS01   | 45 sec         | 62 sec            |

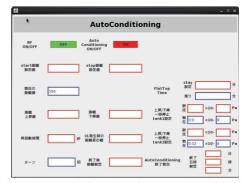

Auto-Conditioning は、限られたマンパワーで空洞コ

ンディショニングを進めるために用意したツールである。空洞の振幅を自動で上下させる動作、真空度が悪化する振幅を維持する動作などを自動で判断するように作り込まれている。現在のシステムではPLCラダー内に実装しているが、ロジックが複雑になってしまい意図しない動作を起こして問題になることが度を更などの割り込み操作が必要なため、開発中のシステムではCohell の script ではなく、java のアプリケーションとして実装する予定である。Figure 4 に現在開発中の Auto-Conditioning の GUI 画面を示す。あくまでもメイン画面とは別のアプリケーションとして実行することで、Auto-Conditioning の動作が終了状態か想定外の停止状態かを容易に確認できるようにして、意図しない動作が起きることを防止したいと考えている。

平成 29 年度の夏季シャットダウン明けの空洞コンディショニングの際に、 開発中の Auto-Conditioning の動作確認をしたいと考えている。

Figure 4: Developing GUI for Auto-Conditioning.

Quick Recovery (以下, QR) は, 空洞が反射, VSWR 及 び Arc で ILK が発報して RF をダウンさせた場合に, 自 動でリセットして RF を復帰させるツールである [4]。 この機能は、RF が完全に落ちて場合は、10 秒程度で空 洞が冷えて共振周波数が変わり、復帰まで時間を要す るのを避けるため用意して、PLC ラダー内に実装して いる。現在のシステムでは PLC が ILK 信号と cPCI に RF-ON/OFF 信号の両方が集約していたためにこのよう な制御が可能であった。一方で、開発中のシステムの RF-ON/OFF 制御は基本的には EPICS 経由で直接新デ ジタイザに命令するため、上記の方法は使えない。 現在 のアイディアは、ILK 発報時は PLC だけで RF-OFF して FastILKでRF-SWを遮断することを想定している。こ のとき、新デジタイザからはRFを出力し続けているが、 RF-SW で止められるというロジックになる。これに関 しては、早急に導入試験を実施する必要があると思って いる。

## 3.5 Auto-Tuner の実現

現在のシステムは、cPCI が離調度とチューナ位置の移動量を算出するが、横河電機 PLC を通してチューナコントローラの制御を実施していた [4-6]。 開発中のシステムでは、新デジタイザがチューナ位置の移動量を算出して、EPICS の OUT フィールド経由でチューナコントローラのレジスタに書き込むことまで実現する予定であ

る。その際に、EPICS compress レコードや sequencer を使用して、平均化する予定である。現在までに、softIOC を使用して平均化した移動量を書き込めることのオフライン試験を実施して、意図通りの動作することまで確認できている。一方で、現在のチューナコントローラの IO は EPICS レコード化されていないため、今後改修する必要がある。この改修を進めて、近々実機の空洞を用いて試験を実施したいと考えている。

#### 3.6 パラメータの保持

現在のシステムでは、PLCがパラメータの現在値を保持していて、電源のオフ/オンにおいても設定値が変化することはない [7]。 開発中のシステムでは、LLRF のパラメータの大半は新デジタイザに対して設定され、PLCはその制御に関与していない。 そこで、新デジタイザのEPICS-IOCには、autosave機能を実装する予定である。現在、オフライン環境下で autosaveをインストールしてソフトウエアの導入試験を実施して、意図した動作することまで確認できた。このパラメータ保持機能に関しては、問題なく実装できると考えている。

#### 3.7 ILK の発報履歴

現在のシステムでは、ILK 発報履歴の管理及び表示には、PLC-TP (GP-Pro)の機能を利用している[7]。開発中のシステムでは、現場には小型 PCと TP 機能付きディスプレイを置いて制御する予定であり PLC-TP が設置されることはない。従って、現在の PLC-TP を使用してILK 発報履歴を管理する方法は採用できない。一方で、QR 機能を使用したときには、EPICS の CA 経由の通信では ILK 発報履歴を取りこぼす可能性を懸念している。そこで、ILK 発報履歴を残すために、横河電機の通信ドライバを使用した方法をメイン画面に実装して、ILK 発報履歴の管理を実現したいと考えている。これに関しては、まだ原理的に可能と構想している段階で、これから導入試験を実施していく予定である。

## 3.8 PLC シーケンス CPU 時刻合せ

現在のシステムでは横河電機のPLCを採用しているが、時刻の変動が問題になる。PLCのシーケンス CPUにはNTPなどの自動時刻補正の機能がないため、開発中のシステムでは C shell scriptと cronコマンドでの1週間に1度程度の自動時刻合せ機能を採用する予定である。PLC時刻合せは、現在のシステムにも共通する問題なので今年度の夏季シャットダウン明けから、このシステムを導入する予定である。

## 4. まとめ

J-PARC リニアックの LLRF システムは開発から 10 年以上が経過している。DFB&DFF を担っている cPCI ボードの生産中止により新しく予備品を購入することができなくなり、また開発環境の維持も困難になってきた。そこで、新規にデジタイザを開発して、システムを更新することを検討している。それに伴い PLC が管理していた機能を別の方法で実現する必要があり、検討を開始している。

将来的には, LLRF デジタイザには J-PARC のイベントタグを付加した上で, 25Hz のデータ収集系を構築し

たいと考えている。また、MPS 発報など異常事象の発生時には、発報前の検波波形を保存する機能を実装していく予定である。

# 参考文献

- Y. Yamazaki for J-PARC accelerator design team, "Technical design report of J-PARC", KEK Report 2003-13 and JAERI-Tech 2003-44; http://www.j-parc.jp

- [2] Z. Fang et al., "Resent Progresses in the LLRF control system of the J-PARC linac", Proc. of the 6th Annual Meeting of Particle Accelerator Society of Japan, Tokai, Aug. 5-7, 2009

- [3] T. Kobayashi et al., "Automatic frequency matching for cavity warming-up in the J-PARC linac digital LLRF control", Proc. of the 6th Annual Meeting of Particle Accelerator Society of Japan, Tokai, Aug. 5-7, 2009

- [4] H. Suzuki et al., "PLC control of J-PARC LowLevel RF System", Proc. of the 4th Annual Meeting of Particle Accelerator Society of Japan, Wako, Aug. 1-3, 2007

- [5] Z. Fang et al., "Development of LLRF control software for the J-PARC 400 MeV linac", Proc. of the 7th Annual Meeting of Particle Accelerator Society of Japan, Himeji, Aug. 4-6, 2010

- [6] Z. Fang et al., "Auto-tuning and Q-value monitoring of RF cavities at the J-PARC linac", Proc. of the 5th Annual Meeting of Particle Accelerator Society of Japan, Hiroshima, Aug. 6-8, 2008

- [7] H. Suzuki et al., "DATA collection using memory area of PLC touch panel for J-PARC Linac RF", Proc. of the 5th Annual Meeting of Particle Accelerator Society of Japan, Hiroshima, Aug. 6-8, 2008