# J-PARC MR における主電磁石 Trim-coil リレー切替装置の EPICS 制御システム EPICS CONTROL SYSTEM FOR TRIM-COIL RELAY-SELECTORS IN J-PARC MR

佐藤健一、五十嵐進、上窪田紀彦、 Kenichi Sato\*, Susumu Igarashi, Norihiko Kamikubota J-PARC center / KEK (Tokai campus)

#### Abstract

In J-PARC main ring, each of the main magnets (Bending, Quadrupole, Sextupole) has a trim-coil. The basic aim of trim-coil is to correct small deviation of each magnetic field. In addition, we have used them for other purposes, for example: (1) in Beam-Based-Alingnment studies, (2) as flux monitors, and (3) to make a short-circuit to reduce ripples of magnetic field. At a moment, trim-coils can be used for only one purpose. We introduced relay-switches to change trim-coil connection to a device, which corresponds to the selected purpose. When we switch the purpose, we have to change 1,200 on-site relays manually, distributed in three buildings. Thus, a control system for trim-coil relay-selectors have been developed in winter, 2014-2015. EPICS tools and environment are used to develop the system. The system comprises PLC I/O modules with controller running EPICS on Linux. The system will be in operation after March, 2015. By using the system, we expect much easier switching of relay-switches than before.

### **1.** はじめに

J-PARC(Japan Proton Accelerator Research Complex) は日本原子力研究開発機構 (JAEA) と高エネルギー加速器研究機構 (KEK) が共同で計画及び運営を行っている大強度陽子加速器施設である。リニアック、3GeV シンクロトロン (RCS: Rapid Cycling Synchrotron)、50GeV シンクロトロン (MR: Main Ring) の 3 つの加速器で構成されており、MR は 2008 年にビーム運転を開始した。[1][2]

MR は周長約 1570m のトンネル内部に設置されている加速器であり、加速器を構成する様々なコンポーネントが設置されている。本発表の対象となるのはそれらのコンポーネントの内、MR の軌道を作り出す主電磁石にまつわる装置である。

## 2. MR 主電磁石

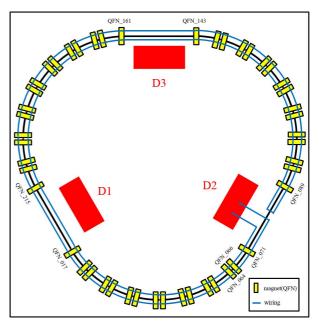

MR における主電磁石には Bending Magnet(BM)、Quadrupole Magnet(QM)、Sextupole Magnet(SM)という種類がある。BM は 96 台、QM は 216 台、SM は 72 台存在し、MR トンネル内で 3 回対称を持って配置されている。主電源はファミリーごとに電源棟に配置され、トンネル 1 周にわたって配置されている各電磁石に配線されている。一例として、QFN という MR における典型的なファミリーの配置図を Figure 1 に示す。Figure 1 からは第 2 電源棟に QFN の主電源があり、最寄りの電磁石から時計回りに MR を一周し、そこから折り返すように配線されていることがわかる。一方、MR トンネルのアドレスの付け方は QM がもとになっている。入射直線部の先頭を 001 番にして反時計回りに割り当てられている。

これらの主電磁石本体にはそれぞれの主コイルに対して Trim-coil が導入されており、この Trim-coil を補助的な役割で様々なことに利用している。例えば、以下に挙げる目的での利用方法がある。ただしそれぞれの用途で使う機器 (電源等) は別途用意する必要がある。

Figure 1: The layout of QFN and cabling.

- a). Beam-Based-Alignment のスタディ

- b). Flux monitor(電場測定)

- c). 加速中のリップルノイズ除去

- d). 電磁石個々のばらつきなどを補正するためのハー モニック補正

この項目の中で特に第3項のリップルノイズ除去に関しては、主電磁石の電源パターンにおける Flat-Top でのみ Trim-coil を short することによって実現している [<sup>3]</sup>。そのため、この用途での Trim-coil の利用法を「Coil-short」と呼ぶ。Coil-short には専用の「Short 基板」を用いるため、Flat-Top を知るための Timing 信号が別途必

<sup>\*</sup> kenichi.sato@j-parc.jp

#### **PASJ2015 WEP106**

要となる。これは MR における遅い取り出しの利用運転に 2012 年から用いられている。

今までは上記にあげた用途を変更する時には Trim-coil に接続する機器を「手作業で」変更していた。そのため一つの電源棟あたり QM だけで 72 台分のコネクタ接続作業時間、および Trim-coil の接続口が MR の 3 つの電源棟に分散しているため各電源棟を周る時間が必要である。この切り替えを簡単になおかつ時間を短縮するために導入されたのが「Trim-coil リレー切替装置」である。

## 3. TRIM-COIL リレー切替装置

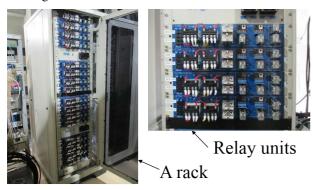

本制御システムを構築する機器をラックに収めた写真を Figure 2 に示す。1 台のユニットには4種の用途の

Figure 2: The photo of a relay selector rack.

ために計8個のリレーがあり、これはTrim-coil2台分に相当する。

このリレー切替装置を制御するための制御システムを、PLC コントローラを用いて EPICS ベースで構築した。J-PARCでは、加速器制御に EPICS(Experimental Physics and Industrial Control System) と呼ばれるツールキットを用いている  $[^{41[5]}$ 。PLC を用いた EPICS ベースの制御システムを構築することで、大量の I/O を 1 つの IOC で構築することができる。更に、I/O コントローラと IOC は 1 つの CPU モジュールに兼任させることにより、低コストおよびシンプルなシステムを狙った。

なお本リレー切替装置の対象となる Trim-coil は QM および SM のみである。BM における Trim-coil に関しては、2015 年現在では用途がリップルノイズ除去のみに限定されているため、リレー切替装置を導入していない。

### 4. 制御システムの構成機器

## 4.1 リレー切替装置の構成

本制御システムは多数のリレーユニットの他に、タイミング分配ユニット、電源制御パネルユニット、UPS を1台ずつで構成されている。また、リレー切替装置の制御システムとして組込み Linux 搭載の PLC コントローラ (F3RP61-2L) および I/O モジュール (YOKOGAWA)  $^{[6][7]}$ を用いる。この PLC コントローラは電源制御パネルユニットの真裏に配置されている。

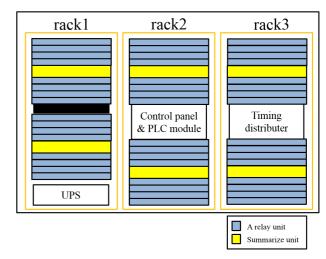

Figure 3 における PLC 出力モジュールは 64ch の信号 点を受け付けるため、リレー信号を 8 ユニットごとに集 約することになる。集約部分は各ラックの上下に 1 つず

Figure 3: The layout of relay selector racks.

つ、合計 6 か所必要になる。これで電源棟 1 つあたり 384 個のリレーを PLC で制御することができる。電源 棟は MR に 3 棟あるので本システムで扱う Trim-coil 切替用のリレーは 1152 個となる。電源の操作やインターロックなどの信号点も含めると、約 1200 個のレコード が必要になる。

#### 4.2 PLC コントローラおよび I/O モジュールの構成

本制御システムにおける EPICS IOC(Input Output Controller) は PLC の CPU モジュールである F3RP61-2L で立ち上げる。F3RP61-2L は組込み Linux のモジュールであり、J-PARC MR では起動時に IOC の設定が自動的に NFS を使って読み込んで使用する <sup>[8]</sup>。本制御システムでリレー切り替え器を制御するために使った PLC モジュールの種類を Table 1 に示す。

Table 1: Selection of PLC I/O Modules

| Slot | Category     | Model     | purpose             |

|------|--------------|-----------|---------------------|

| 1    | CPU          | F3RP61-2L | IOC                 |

| 2    | empty        |           |                     |

| 3    | Din+Dout     | F3WD64-3F | monitor and control |

| 4-9  | Dout         | F3YD64-1P | relay control       |

| -    | bus          | F3BU13-0N |                     |

| -    | power-supply | F3PU30-0S |                     |

Slot 2 は PLC のラダー CPU を挿入する予定であったが、使用しなくてもシステム構築に問題がないことから 当面の間は取り外している。

### 4.3 EPICS レコード作成

リレー切替装置の 324 個のリレーは 6 台の F3YD64-1P モジュールで DO の制御をしている。1 つのリレーがモジュールの1 チャネルに対応している。この手法はシンプルなシステム構築が可能でリレーとチャネルの対応がわかりやすいメリットがある一方で、以下に挙げる事象が発生する可能性がある。

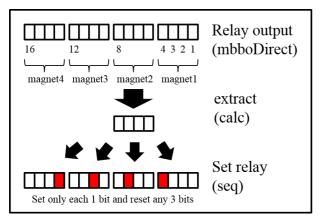

Figure 4: The footnote about records of relay.

- a). リレー素子1つ1つのハード的な Read back が無い

- b). 1 台の Trim-coil に対し複数のリレーが同時に ON にすること

- c). 主電磁石パターン運転中に ON にすること

- d). リレーが ON になっていない用途の機器の出力を ON にすること

これらは想定外の動作を引き起こしたり、場合によっては機器の故障を招くので避けるべき事柄である。そのため、ソフト側で回避するための仕組みが必要である。本システムでは、Read back に関しては電流検出装置を導入する予定とし、その以外は EPICS レコードの組み合わせによってソフト的に実現した。

Table 2 に作成した EPICS レコードと、1 電源棟あたりのおおよその数を示す この Table 2 の「Relay output」

Table 2: The Number of EPICS Records

| record       | type       | number | other               |

|--------------|------------|--------|---------------------|

| status       | bi         | 15     | rack power, timing  |

| interlock    | bi         | 36     | temperture, fan     |

| operate      | bo         | 18     | power and remote    |

| test switch  | bo         | 21     | test and disable    |

| relay output | mbboDirect | 72     | from relay selector |

| bit extarct  | calc       | 288    | 16bit -¿ 4bit       |

| Set relay    | seq        | 1152   | set only 1-bit      |

| Reset relay  | seq        | 288    | reset 4 bits        |

以下に関する補足を Figure 4 を用いて説明する。 Figure 4 では元の 16bit(relay output) から 4bit ずつ抜き出し (bit extarct)、それぞれの bit に対応した Seq レコード (Set relay) を作成している様子が見える。「Set relay」レコードではまず 4bit すべてを OFF にした後、対象となる機器に接続されているリレーのみを ON にしている。 Figure 4 では示されていないが、「Reset relay」は 4bit すべてを OFF にするだけである。この構造にしたのは、PLCの出力チャネルのままでは電磁石のアドレスが一目では分かりずらい事と、電磁石のファミリーの判別が全くで

きない為である。そのため 16bit のレコードを分割した際に、レコード名にファミリーとアドレスを組み込んでいる。

#### 4.4 GUI 画面作成

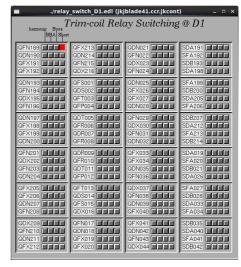

これらのレコードを生成し、操作の為の画面を EDM で作製した。Figure 5 は第1電源棟 (D1) にある Trim-coil

Figure 5: The display of a relay selector based address at D1

リレー切替装置の制御に用いる画面である。この画面ではアドレス 189 番地から 216 を経て 044 番地までのQMと、その区間に相当する SMの Trim-coil に接続する機器を選択できる。同様に第 2 電源棟、第 3 電源棟の分の制御画面も存在する。この画面では 4 種類の用途に切り替えが可能であるが、前述のソフト側の対策を施していないため、使用には注意が必要である。現状では問題があるためメンテナンス用の画面としてごく一部の間で使用される。

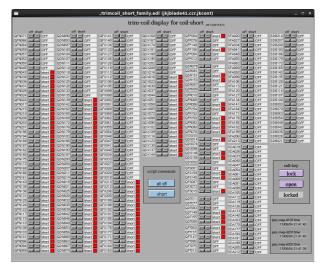

Figure 6: The display of a relay selector based magnet family.

Figure 6 は Coil-short の設定に特化した画面である。

#### **PASJ2015 WEP106**

QM および SM の各ファミリーを電源に近い順番で上から並んでいる。Coil-short する電磁石はどれだけ電源から離れているかを指標とするため、この並び順である必要がある。また、Coil-short 以外の機器に接続するリレーへの Set レコードは必要ないため、最低限の「Reset」と「short」のボタンのみ配置している。その他、この画面では不用意なクリックで操作しないためのソフトキーボタンと、決められた電磁石のパターンを Coil-short するためのシェルスクリプトボタンも用意してある。現状ではパターンを変更したくなった場合にはこのスクリプトを書き換えることになっている。

## 5. 制御システムの動作確認

本制御システムは MR 遅い取り出し運転のスタディまでに間に合うように構築された。2015年2月の通電試験で、制御システムのうち Power/Remote 操作・状態監視に関する動作は確認された。4月3日、リレー全台分の切り替え試験を行い、切替が正常であることがリレーに付随している LED によって確認された。その後、4月9日より遅い取り出し性能試験にて Coil-short のみではあるが連続運転利用を開始した。

今後の予定として、オペレータ向けの確認用画面のブラッシュアップ、CSS(Control System Studio)を使った画面の作成があげられる。特に、現在の画面ではオペレータにとっては情報が多すぎるため、必要十分の情報に集約した画面を作ることが求められている。

## 参考文献

- [1] T. Koseki, et al., "Beam Commissioning and Operation of the J-PARC Main Ring Synchrotron", Progress of Theoretical and Experimental Physics (PTEP) 2012, 02B004, 10.1093/ptep/pts071.

- [2] 日本物理学会誌 2011 年 1 月 (vol. 66 no. 1)、「小特集 大 強度陽子加速器施設 J-PARC~その実現まで~」.

- [3] S. Igarashi, et al., "Magnetic Field Ripple Reduction of Main Magnets of the J-PARC Main Ring using Trim Coils", Proceedings of IPAC '10, Kyoto, Japan, pp301-303, 2010.

- [4] N. Kamikubota, et al., "J-PARC Control toward Future Reliable Operation", ICALEPCS 2011, Grenoble, France, Oct. 10-14, 2011, MOPMS026, pp. 378-381.

- [5] http://www.aps.anl.gov/epics/

- [6] http://www.yokogawa.co.jp/rtos/rtos-index-ja.htm

- [7] J.-I. Odagiri, et al., "Application of EPICS on F3RP61 to Accelerator Control", ICALEPCS 2009, Kobe, Japan, Oct. 12-16, 2009, THD005, pp. 916-918.

- [8] H. Nemoto, et al., "IOC Surveillance System for J-PARC MR Control", (in Japanese), PASJ Annual Meeting in Osaka, Japan, Aug. 8-11, 2012, WEPS118, pp. 745-748.